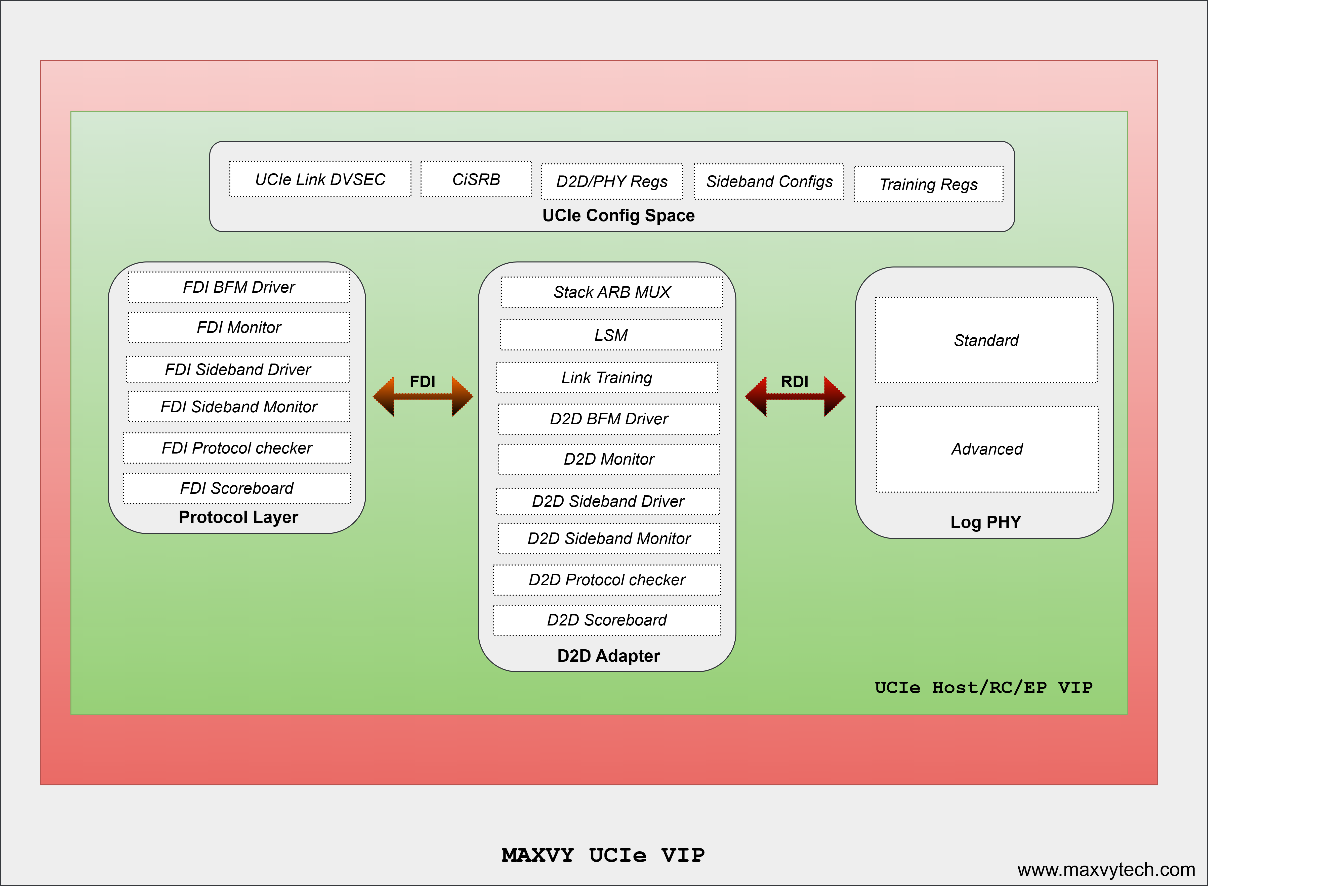

MAXVY UCIe VIP , a state-of-the-art solution that offers a comprehensive set of features and capabilities to ensure the quality and performance of your UCIe designs. MAXVY UCIe VIP is fully compliant with UCIe Specification version 1.0 and supports all the layers of the UCIe stack, such as FDI, RDI, LogPHY, PCIe, and CXL protocols. MAXVY UCIe VIP is also very user-friendly and flexible, with simple APIs, easy integrations, and configurable parameters. You can easily customize and control the UCIe functionality according to your needs. MAXVY UCIe VIP also provides a rich set of verification capabilities, such as protocol checks, functional coverage, traffic generation, error injection, and debug tools. You can easily monitor, detect, and report any issues or violations in your UCIe designs. MAXVY UCIe VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and supports all leading simulators. With MAXVY UCIe VIP, very flexible for unit level testing, you can achieve faster verification closure and higher quality of your UCIe designs.

SL.NO |

Application |

DESCRIPTION |

High Performance Computing (HPC) |

UCIe can be used to connect various chiplets that perform specialized functions, such as compute, memory, I/O, and AI acceleration, to create powerful and efficient HPC systems. UCIe can also enable 3D stacking of chiplets for higher bandwidth and density. |

|

Cloud Computing |

UCIe can be used to create heterogeneous and disaggregated cloud servers that can dynamically allocate resources according to the workload demand. UCIe can also support resource pooling and rack-scale designs with low latency and high performance. |

|

Mobile Devices |

UCIe can be used to create modular and customizable mobile SoCs that can optimize performance, power consumption, and functionality. UCIe can also support integration of different types of chiplets, such as CPU, GPU, memory, RF, and analog. |

|

Automotive Systems |

UCIe can be used to connect various compute blocks and application specific accelators chiplets for automotive applications. |