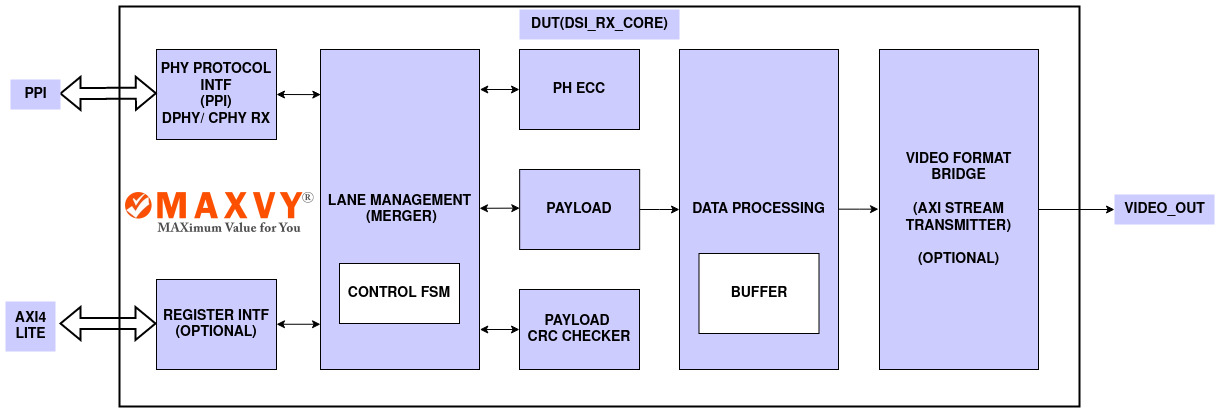

The MAXVY's MIPI DSI-2 RX Controller IP is a fully compliant receive solution designed to interface with MIPI DSI-2 transmitters and deliver display data to SoC video subsystems. The IP supports multi-lane DSI-2 reception over D-PHY and/or C-PHY interfaces through a standard PHY-Protocol Interface (PPI), enabling seamless integration with industry-standard PHY implementations.

The following table describes key features from the MIPI DSI-2 specification that are implemented in the DSI RX IP

Feature Name |

Description |

|---|---|

DSI-2 protocol support |

Fully compatible with MIPI DSI-2 V2.2 specification |

Command mode |

Supports DSI command mode packet reception |

Video mode |

Supports continuous and non-continuous video mode reception |

PPI interface |

Standard PHY-Protocol Interface (PPI) support. Compliant to DPHY V3.5 and CPHY V2.1 |

Multi-lane reception |

Supports 1-lane to 4-lane data reception |

Error detection |

Detects ECC, CRC, and protocol violations |

Processor Interface |

Supports AXI-4 Lite/ APB V2.0 Interfaces for programmability and core status monitoring. |

Pixel unpacking |

Support for all primary and secondary data formats |

Data Interleaving |

Supports Data ID, VC interleaving |

Pixel Modes |

Supports single, dual, and quad pixels per sample |

AXI4-Stream video output |

Standard AXI-Stream interface V1.0 for video data (Optional) |

The RX Controller IP for DSI-2 front module receives 8 bits from each enabled D-PHY data lane via the PPI interface and packs it into the 32-bit datapath for transfer to the DSI-2 protocol module. The D-PHY deskew and ULPS entry/exit conditions are monitored in this module. An optional descrambling block will decode any incoming scrambled data.

The DSI-2 RX Controller IP Protocol module decodes the incoming DSI-2 protocol stream received from the Lane Management module. It performs packet header parsing to extract virtual channel, data type, and word count information, and validates packet headers using ECC checking. For long packets, the module computes and verifies the payload CRC to ensure data integrity.

The DSI-2 RX Controller IP Data Processing and Stream module formats received packet payloads into pixel or packed data suitable for system consumption. The module supports unpacking of standard DSI pixel formats, including RAW, RGB, YUV, and user defined packed formats, and provides configurable pixels-per-clock output.